Adaptive digital anti-noise module based on DSP

Abstract: This paper introduces a digital anti-noise module based on a dedicated DSP chip using a unique software anti-noise algorithm to achieve a speech resolution of no less than 98 in a 120 dB noise environment. This module has been successfully applied to China's airborne communication equipment.

Overview The current third-generation anti-noise products in China use dynamic noise reduction (DNR) technology. DNR technology dynamically adjusts the output voice switch through varying voice peaks for noise reduction. Although it is a better anti-noise analog processing technology, it also has some limitations, including light-tone drop and strong noise tailing; the noise reduction effect is biased towards low frequency; the noise reduction is completely realized by hardware circuit. Problems such as debugging and maintenance are more troublesome. Due to these problems, a large number of popularization and application of analog DNR noise reduction products are limited. With the rapid development of digital signal processing technology, digital anti-noise technology products supported by digital signal processors and their related algorithms continue to emerge. The digital anti-noise module proposed in this paper is the application of modern digital signal processing (DSP) technology and its high-speed real-time processing operation. The corresponding software algorithm is used to process the voice and noise in high noise environment to complete the high noise environment. Voice communication function.

The performance benefits of this module include:

a) The software adopts an adaptive filtering algorithm. The digital anti-noise processor generally suppresses noise by more than 50 decibels, and the output speech is smooth, with no missing words and no noise tailing.

b) The digital anti-noise processor equalizes the noise reduction in the entire voice band (300~3000Hz).

c) The digital anti-noise processor can meet different anti-noise requirements by changing the software algorithm to facilitate product upgrades.

d) Hardware costs are lower than analog DNR products.

e) Using software encryption technology, products are not easy to be infringed or counterfeit, which is beneficial to protect the interests of manufacturers.

Main Indicator Requirements and Overall Solution The digital anti-noise processing module is used as part of the JK-DP10 digital anti-noise processor. It is mainly used for communication in noise environments such as airborne communication terminal equipment. The transmission frequency range is 300~3400Hz. The flatness is not more than 2dB. The noise reduction performance is as follows: the module input terminal adds 3mV, 2 second intermittent sine wave signal (frequency is 300Hz, 700Hz, 1000Hz, 1500Hz, 2000Hz, 2500Hz, 3000Hz) and when adding 3mV, 120dB continuous white noise signal, the module The difference between the output levels is not less than 50 dB.

The first step is to choose a suitable DSP device. Requires low power consumption, high-speed data operation and throughput (40 MIPS or more), including A/D, D/A, and Flash memory (16KB). Then an effective noise model is established, and the adaptive filtering structure and its related software algorithms are designed. Next, design the electromagnetic compatibility (EMC) of the digital anti-noise processor, and select an anti-noise microphone device that can adapt to 120dB ambient noise. The combination of DSP hardware and related software algorithms enables the digital anti-noise processor to achieve a speech resolution of no less than 98 in a 120dB high noise environment.

figure 1

Software and hardware design scheme Main working principle This processor mainly performs high-definition communication function of voice in high noise environment. The voice signal and ambient noise are input to the preamplifier stage through the MIC. The function of the preamplifier stage is to amplify the voice and ambient noise to the A/D recognizable amplitude in the dedicated DSP chip, so that the A/D can normally convert the signal. The analog signal is converted into a 12-bit digital signal by A/D conversion into the DSP's arithmetic unit. The DSP completes testing the ambient noise level and establishes a mathematical model in the first 3 seconds, and then processes the voice and noise according to the given algorithm. The processing result is sent to D/A through the data bus, and is smoothed and sent to the post-amplifier. The function of the post-amplifier is to meet the input requirements of the associated device.

DSP chip selection The JK-DP10 digital anti-noise processor designed in this paper has higher requirements for digital signal processor chips. The chip needs to have strong real-time processing performance, high computation speed and data throughput. It also requires low power consumption. External A/D, D/A and Flash flash memory are best integrated inside the DSP. Reduce product volume. Therefore, one of the TMS320C5XX series DSP chips is selected as the processing chip, and the high-speed A/D, D/A and 32KB Fl ash are used for program loading.

Software Algorithms Digital anti-noise processors are implemented by adaptive filters. The adaptive filter has the ability to track signal and noise variations, so that the characteristics of the filter also vary with signal and noise to achieve optimal filtering.

The characteristic change of the adaptive filter is realized by the adaptive algorithm by adjusting the filter weight coefficient. In general, the adaptive filter consists of two parts, one is the filter structure, and the other is an adaptive algorithm that adjusts the filter coefficients. The structure of the adaptive filter uses an FIR structure. The classical LMS algorithm for in-band white noise processing can not achieve the optimal noise reduction effect, and the autocorrelation property and power spectral density characteristics of noise are also used, and the LMS algorithm can be properly trimmed to achieve the best. Noise reduction effect.

The DSP implementation structure of the digital anti-noise microphone set is shown in Figure 1.

The original input signal d(n) includes the signal and noise, and x(n) is the reference noise input. This adaptive filter essentially completes the noise estimate in d(n) and subtracts the estimated value y(n) from the original channel to achieve the result of noise cancellation, of course, the estimated value y(n) and the original input. The signal is not a simple algebraic subtraction, but a set of corresponding software algorithms, such as power spectrum analysis of the relevant power.

In Figure 1, the adaptive filter uses a lateral structure, and the output y(n) of the filter is expressed as:

N- 1

y(n)= ∑ Wi (n- i)

i =0

N is the order of the filter.

Software Design The complexity of an adaptive filter implementation is usually measured by the number and order of multiplications it requires. The adaptive filter system based on DSP, the data throughput and data processing speed of the DSP chip are also very important. The digital anti-noise processor adopts a 120-order adaptive digital filter, and selects a DSP chip with a computing speed of 40 MIPS as a main processor. Since the DSP chip includes A/D and D/A and 16 KB of flash memory, these On-chip resources make the implementation of adaptive filters more efficient.

According to the autocorrelation property and power density of the noise, in addition to the LMS algorithm in the FIR filter of the traditional symmetric lateral structure, the software also estimates the power spectral density of the noise and the signal, that is, the 16 values ​​of the sampling code. The squared accumulation is performed, and the average power value is obtained, and compared with the previous point power value, and the compared difference is divided by the set noise threshold. If the result is greater than 1, the weight coefficient of the filter is adjusted. Small, the signal output amplitude becomes larger. If the result is less than or equal to 1, the weight coefficient of the filter becomes larger, and the signal output amplitude becomes smaller.

Customized anti-noise DSP chip After the debugging work is completed, it is handed over to a company specializing in DSP chip to make a DSP-specific chip with anti-noise function. After the actual measurement, the power consumption of the whole machine is not more than 70mA, and the lead pin of the DSP chip is reduced to 64 pins, which greatly reduces the area of ​​the Printed Circuit Board. Since the software code is once masked on the chip, the trouble of writing the code every time is eliminated, and the workload of debugging is reduced. Under normal circumstances, the module can be completed by debugging 3 points, which greatly reduces the debugging cost and is beneficial to mass production.

Conclusion The digital anti-noise module uses DSP chips and utilizes adaptive technology to improve the noise immunity of communication products and reduce production costs. This module has been successfully applied to airborne communication equipment in China.

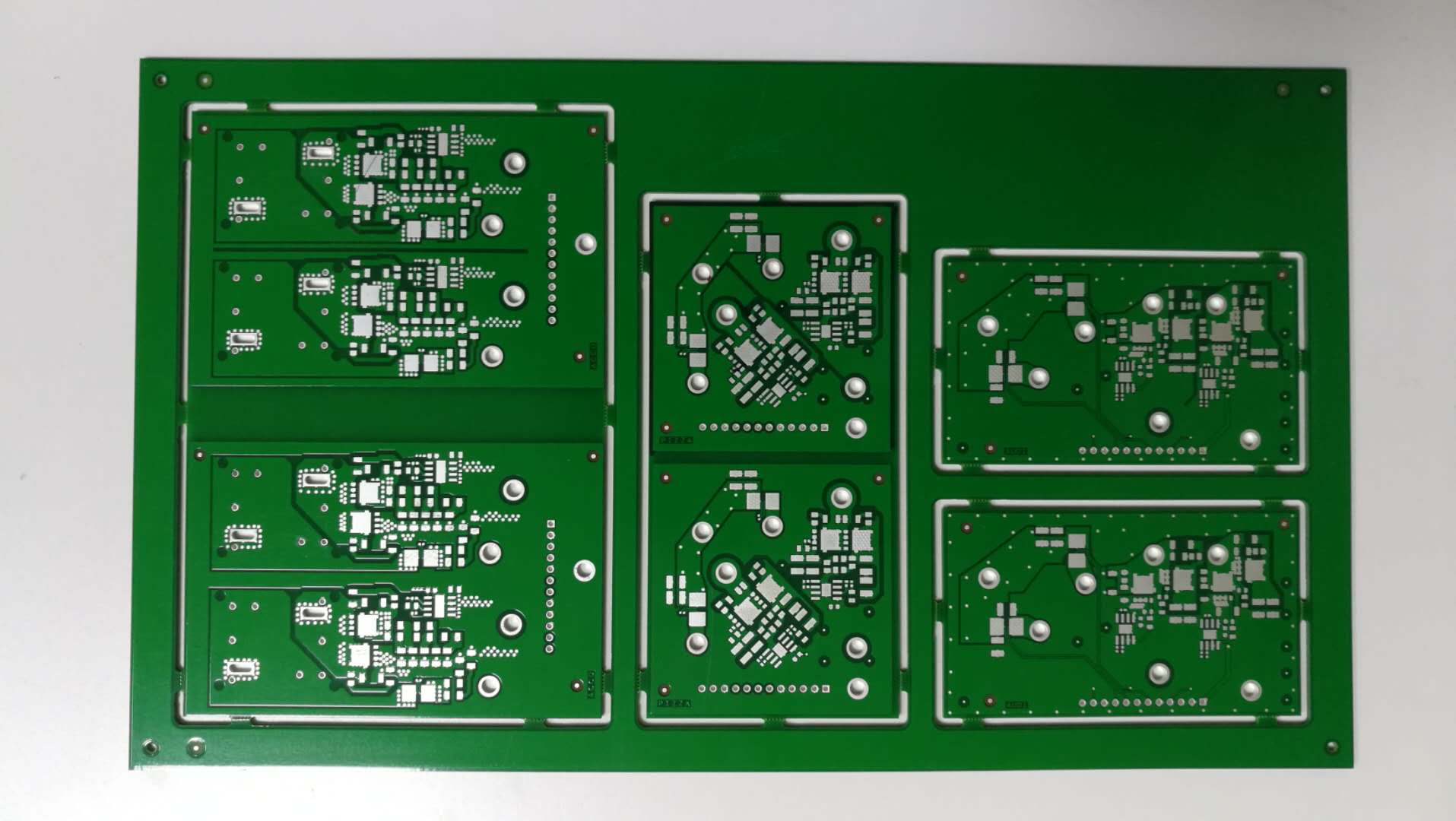

6-layer Thick Copper Power Board.with 5OZ copper both (inner&outer). Base material is S1000-2,FR4 tg170. Total board thickness is 2.5 mm. Min. Hole Size 0.3 mm. Min. line width/Min. line spacing 0.3/0.35 mm. surface treatment is Immersion Tin, covered with green solder mask oil. Mixed-Collage board without X-out. 100% E-test.

The industry calls the inner or outer copper thickness equal or greater than 3 oz. The thick copper circuit boards are mainly used in power supply and high power motors. we can provide 1-10 oz thick Copper Circuit Board.

Thick Copper Power Board

Thick Copper Power Board,Heavy Copper PCB,PCB Copper Thickness,PCB Thickness

Orilind Limited Company , http://www.orilind.com